# Exploiting Errors for Efficiency: A Survey from Circuits to Applications

- 5 PHILLIP STANLEY-MARBELL, University of Cambridge

- 6 ARMIN ALAGHI, University of Washington

12

3

22

31

32

33

- 7 MICHAEL CARBIN, Massachusetts Institute of Technology

- <sup>8</sup> EVA DARULOVA, Max Planck Institute for Software Systems

- 9 LARA DOLECEK, University of California at Los Angeles

- <sup>10</sup> ANDREAS GERSTLAUER, The University of Texas at Austin

- <sup>11</sup> GHAYOOR GILLANI, University of Twente

- <sup>12</sup> DJORDJE JEVDJIC, National University of Singapore

- THIERRY MOREAU, University of Washington

- 15 MATTIA CACCIOTTI, École Polytechnique Fédérale de Lausanne

- ALEXANDROS DAGLIS, Georgia Institute of Technology

- 17 NATALIE ENRIGHT JERGER, University of Toronto

- 18 BABAK FALSAFI, École Polytechnique Fédérale de Lausanne

- 19 SASA MISAILOVIC, University of Illinois at Urbana-Champaign

- 20 ADRIAN SAMPSON, Cornell University

- 21 DAMIEN ZUFFEREY, Max Planck Institute for Software Systems

When a computational task tolerates a relaxation of its specification or when an algorithm tolerates the effects 23 of noise in its execution, hardware, system software, and programming language compilers or their runtime 24 systems can trade deviations from correct behavior for lower resource usage. We present, for the first time, 25 a synthesis of research results on computing systems that only make as many errors as their end-to-end 26 applications can tolerate. The results span the disciplines of computer aided design of circuits, digital system 27 design, computer architecture, programming languages, operating systems, and information theory. Rather 28 than over-provisioning the resources controlled by each of these layers of abstraction to avoid errors, it can be 29 more efficient to exploit the masking of errors occurring at one layer and thereby prevent those errors from propagating to a higher layer. 30

We demonstrate the potential benefits of end-to-end approaches using two illustrative examples. We introduce a formalization of terminology that allows us to present a coherent view across the techniques traditionally used by different research communities in their individual layer of focus. Using this formalization,

34 Authors' addresses: Phillip Stanley-Marbell, University of Cambridge, (phillip.stanley-marbell@eng.cam.ac.uk); Armin 35 Alaghi, University of Washington; Michael Carbin, Massachusetts Institute of Technology; Eva Darulova, Max Planck Institute for Software Systems; Lara Dolecek, University of California at Los Angeles; Andreas Gerstlauer, The University of 36 Texas at Austin; Ghayoor Gillani, University of Twente; Djordje Jevdjic, National University of Singapore; Thierry Moreau, 37 University of Washington; Mattia Cacciotti, École Polytechnique Fédérale de Lausanne; Alexandros Daglis, Georgia Institute 38 of Technology; Natalie Enright Jerger, University of Toronto; Babak Falsafi, École Polytechnique Fédérale de Lausanne; Sasa 39 Misailovic, University of Illinois at Urbana-Champaign; Adrian Sampson, Cornell University; Damien Zufferey, Max Planck 40 Institute for Software Systems. 41

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee

provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and

the full citation on the first page. Copyrights for components of this work owned by others than ACM must be honored.

Abstracting with credit is permitted. To copy otherwise, or republish, to post on servers or to redistribute to lists, requires

prior specific permission and/or a fee. Request permissions from permissions@acm.org.

- <sup>46</sup> © 2020 Association for Computing Machinery.

- 47 0360-0300/2020/5-ART51 \$15.00

- 48 https://doi.org/https://doi.org/10.1145/3394898

- 49

we survey tradeoffs for individual layers of computing systems at the circuit, architecture, operating system, and programming language levels as well as fundamental information-theoretic limits to tradeoffs between resource usage and correctness.

Additional Key Words and Phrases: Approximate computing, error efficiency, cross-layer optimization.

# 55 ACM Reference Format:

Phillip Stanley-Marbell, Armin Alaghi, Michael Carbin, Eva Darulova, Lara Dolecek, Andreas Gerstlauer,

Ghayoor Gillani, Djordje Jevdjic, Thierry Moreau, Mattia Cacciotti, Alexandros Daglis, Natalie Enright Jerger,

Babak Falsafi, Sasa Misailovic, Adrian Sampson, and Damien Zufferey. 2020. Exploiting Errors for Efficiency:

A Survey from Circuits to Applications. ACM Comput. Surv. 53, 3, Article 51 (May 2020), 40 pages. https:

//doi.org/https://doi.org/10.1145/3394898

# 1 INTRODUCTION

Computing systems solve specific computational problems by transforming an algorithm's inputs to its outputs. This, as well as counteracting the effects of noise in the underlying hardware substrate [16, 105, 193], requires resources such as time, energy, or hardware real-estate. Because of the increasing pervasiveness of computing systems and the diminishing returns from performance improvements of process technology scaling [7, 23, 157], resource efficiency is becoming an increasingly important challenge.

Computing systems are reaching the fundamental limits of the energy required for fully-reliable computation [16, 133]. At the same time, many important applications have nondeterministic specifications or are robust to noise in their execution. We dedicate the next section of the review (Section 2) to providing an overview of application domains with quality versus resource usage tradeoffs and we provide two detailed examples in Section 3. They thus do not necessarily require fully-reliable computing systems and their resource consumption can be reduced. For instance, many applications processing physical-world signals often have multiple acceptable outputs for a large part of their input domain. Because all measurements of analog signals have some amount of measurement uncertainty or noise and digital signal representations necessarily introduce quantization noise, it is not always necessary to perform exact computation on data resulting from uncertain measurements of real-world physical signals.

These observations about the fundamental limits of computation and the possibility of trading correctness for resource usage have always been implicit in computing systems design dating back to the ENIAC [233], but have seen renewed interest in the last decade. This interest has focused on techniques to trade precision, accuracy, and reliability for reduced resource usage in hardware. These recent efforts harness nondeterminism and take advantage of application tolerance to coarser discretization in time or value (i.e., precision or sampling rate), to obtain significant resource savings for an acceptable reduction in accuracy and reliability. These techniques have been referred to in the research literature as *approximate computing* and include:

- Programming languages to specify computational problem and algorithm nondeterminism.

- Compilation techniques to transform specifications which expose nondeterminism or flexibility, into concrete deterministic implementations.

- Hardware architectures that can exploit nondeterminism exposed at the software layer, or which expose hardware correctness versus resource usage tradeoffs to the layers above.

- New devices and circuits to implement architectures that exploit or expose nondeterminism and correctness versus resource usage tradeoffs.

In the same way that computing systems that only use as much energy as is necessary are referred to as being *energy-efficient*, we can refer to the computing systems investigated in this survey as being *error-efficient*: they only make as many errors as their end-to-end applications can tolerate [215].

53

54

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

# 99 1.1 Context of this survey

This survey explores research results in hardware and software systems in which the system's 100 101 designers or end-to-end applications can trade lower resource usage for increased occurrence of deviations from correctness. These deviations from correctness may occur within an individual 102 layer of the system (e.g., at the circuit layer), or they may occur in the context of an end-to-end 103 computing system application (e.g., a microcontroller-based pedometer application driven by sensor 104 measurements from an accelerometer). Existing related surveys [10, 77, 145, 149, 191, 235] present 105 valuable analyses of techniques at subsets of the layers of computing systems. These existing 106 107 surveys provide complementary coverage of the relevant literature but neither introduce any broadly-applicable mathematical formalization of the research problem, nor do they survey the 108 information-theoretic foundations of the tradeoffs between resource usage and correctness like we 109 do in this article (Section 4 and Section 10, respectively). 110

This survey is the result of research ideas and discussions started at a multi-disciplinary workshop, involving the authors, held in April 2017. We wrote the survey shortly thereafter and submitted it for review in June 2018. As a result, our coverage of the research literature is skewed towards articles published prior to 2018. We have made every attempt to update the survey with relevant recent results at the time of acceptance for publication.

Any survey of an active research field can necessarily never be exhaustive. We do not explicitly cover the long history of fundamental research results on changing the structure of algorithms to trade, e.g., average case performance for deterministic execution (approximation and randomized algorithms). Instead, we limit ourselves to results that apply to compile-time program transformations of applications which implement a fixed algorithm. Throughout the survey, our objective is to highlight representative examples that provide reusable insights, rather than compile an exhaustive list of all related publications and related domains.

# 1.2 Contributions and outline

This survey presents:

- A cross-disciplinary overview of research results on correctness versus resource usage tradeoffs, spanning the hardware abstractions and disciplines of: transistors, circuits, microar-chitecture and architecture, programming languages, operating systems, and applications.

- An overview of existing uses of quality-versus- resource-usage tradeoffs across application domains and examples of two end-to-end applications (Section 2 and Section 3).

- Mathematical formalization and terminology for describing resource usage versus correctness tradeoffs of computing systems that interact with the physical world. The formalization is consistent with existing widely-used terminology and at the same time provides a coherent way to discuss tradeoffs across domains of expertise (Section 4).

- Detailed discussions of the state of the art across the layers of system implementation stack, from circuits, to microarchitecture and architecture, to the programming language and operating system layers of abstraction (Section 5 Section 8).

- A taxonomy tying together the ideas introduced in the survey (Section 9).

- A discussion of limits of computation in the presence of noise. (Section 10).

- A set of open challenges across the layers of abstraction (Section 11).

# 1422EXISTING QUALITY VERSUS RESOURCE USAGE TRADEOFFS

The idea of trading quality for resources and efficiency is inherent to all computing domains. Several research communities have developed techniques to exploit tolerance of applications to noise, errors, and approximations to improve the reliability or efficiency of software and hardware systems. In the same way that there have always been attempts to make hardware and software

147

123

124

125

126

127

128

129

130

135

136

137

138

139

more tolerant to faults independent of specific research on fault-tolerant computing, there has

also always been a pervasive use of techniques for approximation (e.g., Taylor series expansions)

independent of recent interest in approximate computing. The following highlights some of these

efforts across application domains.

# 153 2.1 Scientific computing

Scientific computing can be defined as "the collection of tools, techniques, and theories required to

solve on a computer mathematical models of problems in science and engineering" [71]. Most of

these models are real-valued, and exact analytical solutions rarely exist or are costly to compute [44,

134]. As a result, numerical approximations and their associated quality-efficiency tradeoffs have

always been important in scientific computing [55].

These numerical approximations are introduced at different levels of abstraction. Because the real-world is too complex to be represented exactly, practical considerations require resorting to models, incurring modeling errors [134]. Even with a model in hand, analytical solutions may not exist and numerical solutions are needed to approximate the exact answers [26, 47], introducing further deviations from the expected result. And finally, most models are real-valued and thus have to be approximated by finite-precision arithmetic, adding roundoff errors [85].

Roundoff errors can be bounded to some extent automatically using techniques such as interval arithmetic [104]. Dealing with most of the errors introduced by modeling, numerical approximation, and finite-precision arithmetic, is rarely automated by software tools. The state of the art in dealing with modeling and numerical errors often requires manual intervention of the programmer or domain expert and is typically on a per-application basis. Because of the resulting complexity of the error analysis, the resulting error bounds are often only asymptotic.

# 2.2 Embedded, digital signal processing, and multimedia systems

Many computing systems that interact with the physical world or which process data gathered from it, have high computational demands under tightly-constrained resources. These systems, which include many embedded and multi-media systems, must often process noisy inputs and must trade fidelity of their outputs for lower resource usage. Because they are designed to process data from noisy inputs, such as from sensors that convert from an analog signal into a digital representation, these applications are often designed to be resilient to errors or noise in their inputs [213].

Several pioneering research efforts investigated trading precision and accuracy for signal processing performance [7] and exploiting the tolerance of signal processing algorithms to noise [83, 192]. When the outputs of such systems are destined for human consumption (e.g., audio and video), common use cases can often tolerate some amount of noise in their I/O interfaces [207–209, 212, 214].

# 2.3 Computer vision, augmented reality, and virtual reality

Many applications in computer vision, augmented reality, and virtual reality are compute-intensive.

As a result, many of their algorithms (e.g., stereo matching algorithms) have always been imple mented with quality versus efficiency tradeoffs in mind [72, 187, 222]. The implementations of these

algorithms have used techniques including fixed-point implementations of expensive floating-point

numerics [135] and algorithmic approximations such as removing time-consuming backtracking

steps [24] when implementing these algorithms on FPGA accelerators.

# 191 2.4 Communications and storage systems

The techniques we survey often involve computation on noisy inputs or data processing in the presence of noise in much the same way research in communication systems and information theory considers communication over a noisy channel. As one recent example of work that could be viewed as either traditional information theory and communication systems research or approximate

196

152

171

172

173

174

175

176

177

178

179

180

181

182 183

190

Publication date: May 2020.

computing, Huang et al. [90] present a simple yet effective coding scheme that uses a combination 197 of a lossy source/channel coding to protect against hardware errors for iterative statistical inference. 198

#### Big data and database management systems 2.5

Approximate query processing in the context of databases and big data research leverages sampling-202 based techniques to trade correctness of results for faster query processing. Early work in this 203 direction investigated sampling from databases [153, 154]. More recently, BlinkDB [2], an ap-204 proximate query engine, allows users to trade accuracy for response time. BlinkDB uses static 205 optimizations to stratify data in a way that permits dynamic sampling techniques at runtime to present results annotated with meaningful error bars. Other recent efforts include Quickr [101] and ApproxHadoop [69]. 208

#### 2.6 Machine learning

199 200

201

206

207

209

211

224

210 Machine learning techniques learn functions (or programs) from data and this data is in practice either limited or noisy. Larger datasets typically lead to more accurate trained machine learning 212 models, but in practice training datasets must be limited due to constraints on training time. As 213 a result, many machine learning methods must inherently grapple with the tradeoffs between 214 efficiency and correctness of the systems. 215

There are several techniques that allow machine learning systems to trade accuracy for effi-216 ciency. These techniques include random dropout [203], which randomly removes connections 217 within a neural network to prevent overfitting during training and to improve overall training 218 accuracy. Techniques such as weight de-duplication and pruning [37, 79], low-intensity convolution 219 operators [89, 92], network distillation [174], and algorithmic approximations based on matrix 220 decomposition [50, 110] take advantage of redundancy to minimize the parameter footprint of a 221 given neural network. Weight quantization is yet another technique to reduce computation and 222 data movement costs in hardware [45, 97]. 223

#### **Approximation and Randomized Algorithms** 2.7 225

Approximation has been studied extensively in algorithmics and theoretical computer science. 226 Approximation algorithms seek efficient solutions to computationally hard problems (e.g., knapsnack 227 or SAT solving), such that the distance of the approximate solution is guaranteed to be within a 228 fixed bound from the exact solution [228, 234]. These algorithms often use heuristic search methods 229 (e.g., greedy search), or relax hard optimization problems to instances of linear programs. Often, 230 they are *fully polynomial-time approximation schemes*—polynomial-time algorithms that for each 231 fixed error bound  $\varepsilon$  have their running time bounded by a polynomial in the size of  $\frac{1}{c}$  and the size 232 of the problem. 233

Randomized algorithms use a sequence of random bits to achieve good average case performance 234 over the input space. These algorithms often ensure that the computed solution is within a small 235 distance from the exact solution with high probability [146]. Especially interesting is the class of 236 randomized algorithms that perform property testing, i.e., fast randomized algorithms for decision-237 making [70]. Examples include testing for similarity of strings or almost-sortedness of a sequence's 238 elements. These algorithms typically query only a small fraction of the data set (often logarithmic 239 in size), and make the correct decisions with high probability. 240

These approximations are purely algorithmic in nature. They often come with strong theoretical 241 guarantees, but do not take advantage of approximation opportunities in the system stack. Each 242 of these topics have been extensively covered by existing monographs, e.g., [70, 146, 228, 234], to 243 which we refer the interested readers. 244

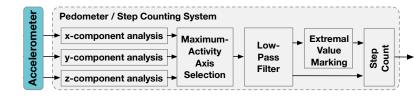

Fig. 1. The block diagram of one canonical pedometer application implementation.

# 3 ILLUSTRATIVE END-TO-END EXAMPLES

Many applications from the domains of signal processing and machine learning have traditionally had to grapple with tradeoffs between precision, accuracy, application output fidelity, performance, and energy efficiency (see, e.g., Section 2.2 and Section 2.6). Many of the techniques applied in these domains have been reimagined in recent years, with a greater willingness of system designers to explicitly trade reduced quality for improved efficiency.

We discuss two applications from the signal processing and machine learning domains: a pedometer and digit recognition. Using these examples, we suggest ways in which resource usage versus correctness tradeoffs can be applied across the layers of the hardware stack, from sensors, over I/O, and to computation. We use these applications to demonstrate how end-to-end resource usage could potentially be improved even more when tradeoffs are exploited at more than one layer of the system stack.

### 3.1 Example: a pedometer application

Applications which process data measured from the physical world must often contend with noisy inputs. Signals such as temperature, motion, etc., which are analyzed by such sensor-driven systems, are usually the result of multiple interacting phenomena which measurement equipment or sensors can rarely isolate. At the same time, the results of these sensor signal processing applications may not have a rigid reference for correctness. This combination of input noise and output flexibility leads to many sensor signal processing applications having tradeoffs between correctness and resource usage.

One concrete example of such an application is a pedometer (step counter). Modern pedometers typically use data from 3-axis accelerometers to determine the number of steps taken during a given period of time. Even when a pedometer's wearer is nominally motionless, these accelerometers will detect some distribution of (noisy) measured acceleration values. At the same time, small errors in the step count reported by a pedometer are often inconsequential and therefore acceptable.

Figure 1 shows a block diagram for an implementation of one popular approach [242]. Our 280 implementation takes as input 3-axis accelerometer data and returns a step count for time windows 281 of 500 ms. The pedometer algorithm first selects the accelerometer axis with the maximum peak-282 to-peak variation (the maximum activity axis selection block in Figure 1). The algorithm uses the 283 selections to create a new composite sequence of accelerometer samples. Next, the pedometer 284 algorithm performs low-pass filtering, and then, for each 500 ms window, computes the maximum 285 and minimum acceleration values and the midpoint of this range (the extremal value marking block 286 in Figure 1). Finally, the algorithm counts how many times the low-pass filtered signal crosses the 287 per-window midpoints in one direction (e.g., from above the midpoint to below it), and it reports 288 this count as the number of steps. 289

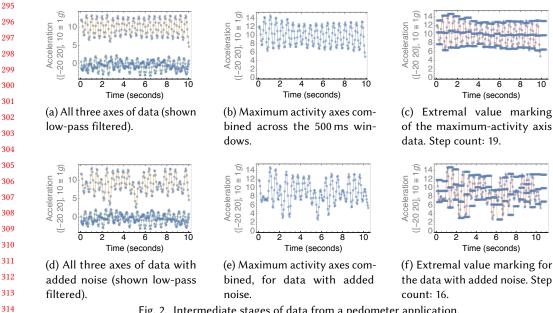

Figures 2a-2c show the progression of a sequence of accelerometer samples through the stages of the pedometer algorithm, which outputs a step count of 19 at the end. Figures 2d-2f show a modified version of the data where we have replaced 5% of the samples with zeros to simulate intermittent failures at a sensor. Even though the data in the final stage of the algorithm (Figures

246

247

248

249

250 251

252 253

266

267

Fig. 2. Intermediate stages of data from a pedometer application.

2c and 2f) looks qualitatively different, the final output of the algorithm is relatively close the noise-free output.

Applying individual tradeoffs. The hardware and system stack for a typical pedometer comprises sensors (e.g., accelerometers), I/O links (e.g., SPI or I2C) between those sensors and a processor, a runtime or embedded operating system, the implementation of the pedometer algorithm, and a display. A system's designer may exploit the resource versus correctness tradeoffs at each of these layers or components independently, using the techniques surveyed in Sections 5-8 of this article. For example, a system designer could apply Lax [213] to sensors, VDBS encoding [208, 209, 214] to the I2C or SPI communication between sensors and a microcontroller, and could ensure that the potentially inexact data does not affect the overall safety of the application using EnerJ [180] or FlexJava [158].

Potential for end-to-end optimization. This survey argues for exploring the end-to-end combination of techniques for trading correctness for efficiency, across the levels of abstraction of computing systems. Rather than treating each layer of the hardware and system software stack as an independent opportunity, this article argues that greater resource-correctness tradeoffs are possible when the entire system stack is considered end-to-end. For example, the insensitivity of the pedometer algorithm to input noise highlighted in Figure 2 might be determined by program analyses. These analyses could in turn be used to inform instruction selection for generated code as well as determining sensor operating settings (e.g., sampling rate, operating voltage, on-sensor averaging) and sensor I/O settings (e.g., choices for the I/O encoding for the sensor samples as they are transferred from a sensor).

#### **Example: digit recognition** 338 3.2

Digit recognition is the computational task of determining the correct cardinal number correspond-339 ing to an image of a single handwritten digit. Digit recognition is to computer vision scientists what 340 fruit flies are to biologists: a quick and easy way to evaluate the feasibility of a novel idea. One can 341 envision a simple system that analyses handwritten digits directly from a camera source. An image 342

343

315 316

317

318

319

320

321

322

323

324

325

326

327

328

329

330

331

332

333

334

335

336

### Stanley-Marbell et al.

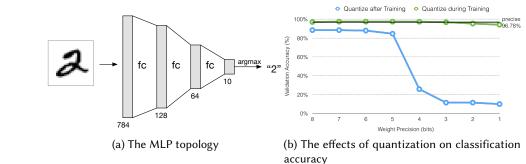

Fig. 3. The multi-layer perceptron (MLP) trained on the MNIST dataset: topology and effects of quantization.

is captured by a CCD or CMOS sensor. Each pixel of the image is converted from an analog reading to a quantized value in the digital domain. That raw digital image is now sent for processing to a processor or dedicated ASIC to produce a cardinal number that preferably matches the ground truth handwritten digit. Such system could be used to label postal codes in an automated mail sorting facility. The inherent analog nature of the processing system's camera sensor, combined with the imperfect shapes of the human-written numerals, make digit recognition a fundamentally noisy and error-prone process.

One popular technique used to classify digits is the use of neural networks [116]. Neural net-365 works are trained with a correctly labeled training data set, which is used to iteratively improve 366 classification accuracy via the back propagation algorithm. Neural networks—and more broadly 367 machine learning-are well suited for object recognition problems due to the fact that it would 368 be very difficult to write a program describing how to classify an image based on highly diverse 369 ground-truth examples. Instead, neural networks learn from training examples as a human would 370 do, and derive internally a set of features that can help discriminate between the different classes 371 of objects. 372

Neural networks are naturally imperfect discriminators: the quality of the classification relies 373 upon how diverse the training set is, and how resilient the classifier is to noise and input modifica-374 tions (e.g. rotations, lateral shifts, etc.). In addition, if the classifier is trained for too long over a 375 dataset that is too limited, it can end up overfitting the training set. Errors that occur as bit-flips 376 internally can be learned around during training in order to gracefully recover from hardware 377 errors [53]. Aggressive quantization techniques such as network binarization [46, 168] can work 378 well in certain domain problems. Randomized pruning techniques can also provision against over-379 fitting, and help improve the trained classifier's robustness [117]. Consequently, neural networks 380 constitute an ideal target for approximation techniques across the stack. 381

Figure 3(a) shows a simple network architecture for performing handwritten digit recognition. 382 The network consists of three fully-connected layers (labeled "fc" in the Figure). The input layer 383 takes in a 28×28 image, which is flattened into a one-dimensional array of 784 pixel values. Each 384 fully connected layer performs a weighted sum of all input values to produce a single output value 385 that is applied a bias, followed by a non-linear activation function. The latter determines if the 386 output neuron should be considered active or not. The layers before the final output layer are 387 known as hidden layers: they identify hidden features that help discriminate between different 388 classes of digits. The final layer has 10 outputs, each corresponding to a different class of digits. 389 The neuron with the highest value determines what digit the neural network has classified the 390 input image as. 391

344

345

346

347

348

349

350

51:8

362

363

364

# Exploiting Errors for Efficiency: A Survey from Circuits to Applications

|      | Default 2's Complement Encoding |                   |                   |                  | Error-Aware Ternary Encoding |       |                  |                  |                  |                   |

|------|---------------------------------|-------------------|-------------------|------------------|------------------------------|-------|------------------|------------------|------------------|-------------------|

| Bits | Value                           | b0 stuck at 0     | b0 stuck at 1     | b1 stuck at 0    | b1 stuck at 1                | Value | b0 stuck at 0    | b0 stuck at 1    | b1 stuck at 0    | b1 stuck at 1     |

| 00   | 0                               | 0 (Δ=0)           | 1 ( <b>Δ</b> =1)  | 0 (Δ=0)          | -2 ( <b>Δ</b> =2)            | 1     | 1 ( <b>Δ</b> =0) | 0 ( <b>Δ</b> =1) | 1 ( <b>Δ</b> =0) | 0 (Δ=1)           |

| 01   | 1                               | 0 (Δ=1)           | 1 ( <b>Δ</b> =0)  | 1 ( <b>Δ</b> =0) | -1 ( <b>Δ</b> =2)            | 0     | 1 ( <b>Δ</b> =1) | 0 (Δ=0)          | 0 (Δ=0)          | -1 (Δ=1)          |

| 10   | -2                              | -2 ( <b>Δ</b> =0) | -1 ( <b>Δ</b> =1) | 0 ( <b>Δ</b> =2) | -2 ( <b>Δ</b> =0)            | 0     | 0 (Δ=0)          | -1 (Δ=1)         | 1 ( <b>Δ</b> =1) | 0 (Δ=0)           |

| 11   | -1                              | -2 (Δ=1)          | -1 (Δ=0)          | 1 ( <b>Δ</b> =2) | -1 (Δ=0)                     | -1    | 0 ( <b>Δ</b> =1) | -1 (Δ=0)         | 0 (Δ=1)          | -1 ( <b>Δ</b> =0) |

Fig. 4. Application-aware codes can be critical in enabling robustness to errors in neural networks. In the case of ternary neural networks, we can craft codes that ensure a deviation of at most 1 from the original value when a single bit flip error occurs.

Applying individual tradeoffs. Figure 3 (b) shows the results for accuracy of the neural network with quantization of weights starting with a 32-bit floating point baseline all the way down to a 1-bit weight. The network is trained on the MNIST data set with quantization of weights either during or after training. The results show that as long as re-training is applied, this neural network is extremely tolerant even to aggressive levels of quantization. Quantization additionally enables weight prunability and compressibility: weights represented with fewer bits lead to fewer distinct values, and more weights end up in the zero-valued bin. This creates opportunities for sparse matrix compression [78], which can be directly implemented in hardware.

*Potential for end-to-end optimization.* Once the network has been quantized and compressed, we can further leverage resource versus correctness tradeoffs by storing the weights in approximate voltage-overscaled SRAM cells [169], which occasionally produce read errors. Recent work [108] motivate the use of approximate SRAMs by highlighting that they consume a significant percentage of overall power in accelerator. The authors show that both re-training and fault detection mechanisms can mitigate the destructive effects of voltage-overscaled SRAM read upsets on classification tasks.

In addition, in the case where weights are quantized to -1, 0 and 1, choosing the right encoding shown in Figure 4 can ensure that the effects of a single bit-flip due to an erroneous read remains limited. With this encoding, single bit-flip errors would cause in the worst case a deviation of 1 from the original weight value, as opposed to a value polarity flip from -1 to 1 or vice-versa. The latter is allowed under the default 2's complement encoding, and could potentially lead to catastrophic classification degradation.

To conclude, a synergistic combination of (1) training-corrected quantization and pruning, (2) hardware optimization of SRAMs to minimize power via voltage overscaling, and (3) selecting a weight encoding that minimizes catastrophic bit-flips altogether enables a more efficient digit classification system that can embrace the noisy nature of the image capturing system and the variable nature of handwritten digits.

### 4 TERMINOLOGY

The terminology used to describe resource usage versus correctness tradeoffs has historically differed across research communities (e.g., the computer-aided design and design/test communities versus the programming language and system software communities). The differences in terminol-ogy are sometimes inevitable: a "fault" in hardware is usually a stuck-at logic- or device-level fault while a "fault" in an operating system is usually the failure of a larger macro-scale component. In this article, we attempt to provide a uniform scaffolding for terminology. In doing so, we acknowl-edge that this terminology will by necessity need to be reinterpreted when applied to the different layers of abstraction in a computing system and we do precisely that at the beginning of each of the following sections.

51:9

# 442 4.1 Computation in the physical world

We consider computing systems that make observations of the physical world (e.g., using sensors or other data input sources) and compute a discrete set of actions that the system (or a human) then applies back to the physical world. Such end-to-end systems are therefore *analog in, analog out*. In this process, the computing system *measures* the physical world, *computes* on a sample of its measurement, and then computes a set of *actions or actuations* to be applied to the world. Figure 5 shows the steps of computation in the physical world.

We denote the domain of quantized values by  $\mathbb{Q}$ . In practice, quantized values are often bounded integers or finite-precision floating-point numbers. When working with a relation  $r \subseteq A \times B$ , the domain and range of a relation r are defined as  $Domain(r) := \{x \mid \exists y.(x, y) \in r\}$  and Range(r) := $\{y \mid \exists x.(x, y) \in r\}$ . The composition of two relations f and g, denoted  $f \circ g$ , is allowed if  $Range(f) \subseteq$ Domain(g) and it is defined as  $f \circ g = \{(x, z) \mid \exists y.(x, y) \in f \land (y, z) \in g\}$ . A *left-total* relation is a relation that covers all members of its input domain. In other words, an output exists for every possible input.

**Physical world:** We assume that all of our systems are situated in the physical world and we model inputs from this world with real numbers,  $\mathbb{R}$ . This assumption is consistent with most applications that trade errors for efficiency (see Section 2 and Section 3), such as sensing applications (as in Section 3.1), cyber-physical systems, computer graphics, computer vision, machine learning (as in Section 3.2), and scientific computing.

461 **Measurement and analog processing step:** Each computation situated in the physical world 462 begins with a *measurement* in which the computing system makes an observation of the physical 463 world. In metrology, this quantity is referred to as the *measurand*. We denote the result of a 464 measurement by a probability distribution. We restrict our focus to distributions that we can 465 represent with a *probability density function (PDF)*,  $f : \mathbb{R} \to \mathbb{R}$ .

Measurements may include within their internal processes computations that transform the 466 measured distributions to yield new distributions. These internal processes may be nondeterministic. 467 We include this facility to account for systems that may perform computation directly in the 468 unsampled and unquantized analog domain and Section 5.3 of the survey gives examples of such 469 systems. A measurement is therefore a function of type  $f : \mathbb{R} \to (\mathbb{R} \to \mathbb{R})$ , mapping a real value 470 (the measurand) to a function in the form of the probability distribution (the measurement). The 471 result of the measurement step of a computation is therefore still in the domain of continuous-time 472 real-valued quantities. 473

**Sampling and quantization step:** Between the measurement step and a subsequent discrete (digital) computation step, we assume that there is a sampling and quantization step that generates discrete-time samples with discrete values from the real-valued distribution resulting from the measurement step. A *sampler* is therefore a relation  $f : (\mathbb{R} \to \mathbb{R}) \times \mathbb{Q}^m$  that samples and quantizes a discrete value from a probability distribution. ( $\mathbb{Q}^m$  denotes the set of allowable quantized values.) The process of quantization adds an implicit noise, known as the *quantization noise* to the real-valued input.

**Digital computation step:** In the discrete world, we consider the computations that take as input a discrete sample from the measured world and performs a potentially nondeterministic computation to produce a discrete output. Therefore, a discrete computation f is a left-total relation  $f \subseteq \mathbb{Q}^m \times \mathbb{Q}^o$  where  $\mathbb{Q}^m$  is the input and  $\mathbb{Q}^o$  is the output.

**Actuation step:** The digital outputs can be used back in the physical world as inputs to real-valued actuation which modifies the state of the physical world. An actuation computation is therefore a nondeterministic function that we model as a left-total relation  $f \subseteq \mathbb{Q}^o \times \mathbb{R}$ .

51:10

485

486

Fig. 5. Steps of computation in the physical world.

### 500 4.2 Computation and correctness

491

492

493

494

495

496

497

498 499

539

Following the terminology defined in Section 4.1, we can express any computation that processes

data from the physical world as a composition of the steps of measurement, sampling and quantiza tion, digital computation, and actuation. Each of these steps defines a *computation*:

**Computation:** A computation f is a nondeterministic function that we denote as a left-total relation  $f \subseteq \mathbb{I} \times \mathbb{Q}$  where we instantiate the domain  $\mathbb{I}$  and  $\mathbb{O}$  to fit the computation's corresponding step from Section 4.1. For example, as we will see later in Section 5.1, at the circuit level, the input domain  $\mathbb{I}$  and the output domain  $\mathbb{O}$  are voltage levels.

We model computations as left-total relations to account for nondeterminism where for the same input, the computation may produce different outputs on different executions. The relations are left-total in that there exists at least one output for every value in the input domain. This modeling assumptions also dictates that computations terminate. If a computation is deterministic, then we model it as a function  $f : \mathbb{I} \to \mathbb{O}$ .

**Specification:** For any computation  $f \subseteq \mathbb{I} \times \mathbb{O}$ , a system's developers and users can provide its *specification* as a relation  $f^* \subseteq \mathbb{I} \times \mathbb{O}$  that defines the set of *acceptable* mappings between the function's inputs and outputs. A specification need not be executable itself and multiple implementations can satisfy the same specification.

**Correctness:** A computation and its corresponding definition as a relation is *correct* if it *implements* its specification. A computation f implements a specification  $f^*$  iff  $\forall i, o. (i, o) \in f \Rightarrow$  $(i, o) \in f^*$ . This definition means that every output of f for a given input, must be valid according to the specification.

Faults: To define faults, we first decompose a computation f into two computations  $g \subseteq \mathbb{I} \times \mathbb{M}$ and  $h \subseteq \mathbb{M} \times \mathbb{O}$ , where  $\mathbb{M}$  is a domain of values for the output of g and  $h \circ g \equiv f$ . Given this decomposition, a *fault* is an anomaly in the execution of g on an input i such that g produces an anomalous, unexpected value m in that  $(i, m) \notin g$ .

**Errors:** An error occurs when a computation encounters a fault and the computation's resulting output does not satisfy its specification. Given a computation f and its decomposition into g and has above, the semantics of an error is that if the execution of g on i produces a faulty value m (as above), then that fault is an error if the result of the continued execution via h does not satisfy f's specification – namely, that  $(i, h(m)) \notin f^*$ .

**Masking:** A fault does not always result in an error; a fault can instead be *masked*. If a computation encounters a fault and the computation's resulting output satisfies its specification, then the fault has been masked by the computation's natural behavior. Given a computation f and its decomposition into g and h as before, the semantics of a masked error is that if the execution of g on i produces a faulty value m (as above), then that fault is masked if the result of the continued execution via h satisfies f's specification – namely, that  $(i, h(m)) \in f^*$ .

**Precision and accuracy:** We define *precision* as the degree of discretization of the state space determined by  $\mathbb{Q}^m$  (from the sampling and quantization step, Section 4.1) and we define *accuracy* as a distance between the functions f and  $f^*$  defined above.

#### 4.3 Standard viewpoints 540

Let *h* be the identity function and f = q. Then the aforementioned definitions give a semantics to 541 faults that affect the output of a single, monolithic function f. Take  $f^*$  to be f, then the function's 542 specification is given by its exact behavior. This form of specification is the standard assumption 543 for computing systems wherein they must preserve the exact semantics (up to nondeterminism) of 544 the computation. Most existing approaches to trading errors for efficiency fit this viewpoint: they 545 typically start from an existing program as their specification and approximate it to allow for more 546 efficient implementations. 547

#### 548 4.4 **Ouantifying errors**

549 Approaches to quantifying errors include absolute errors, relative errors, and error distributions. In 550 most contexts, the evaluator of a system is interested in the error of not only a single input, but 551 a whole domain of inputs. Depending on the application domain, upper or lower bounds on the 552 worst-case error, or average errors may be of interest. When a computation runs repeatedly, the 553 error frequency or error rate captures how often a computation returns an incorrect result. 554

#### TRANSISTOR-, GATE-, AND CIRCUIT-LEVEL TECHNIQUES 5 555

Transistors provide the hardware foundations for all computer systems. As a result, their physical 556 properties determine the efficiency at which a particular computation can be performed. When 557 collections of transistors are used to form gates and analog circuits, and when collections of gates 558 are used to implement digital logic circuits, the organization of the transistors, gates, and circuits 559 can be designed to trade efficiency for correctness. 560

#### 561 5.1 Notation

569

571

562 Following the notation introduced in Section 4, input I can be defined as a voltage level that is 563 switched to  $\mathbb{O}$  as a computation f is executed. Therefore,  $f: \mathbb{I} \to \mathbb{O}$  is a switching of voltage at a 564 transistor or a group of transistors forming a circuit element, for instance, a byte in a memory or 565 an adder in an arithmetic/logic unit (ALU). Such computation can be regarded as  $f^* : \mathbb{I} \to \mathbb{O}$  where 566 the relation between  $f^*$  and f is the difference in the electrical operating points of the individual 567 transistors. This difference saves computational costs like power consumption and latency while 568 introducing timing errors and incorrect voltage levels.

#### 5.2 Analog input / analog output systems: a comparison reference for quantization

570 When using finite-precision arithmetic, computation always involves errors that are caused by quantization. Quantization is a fundamental mechanism for trading energy for accuracy and recent 572 work has highlighted examples of its effectiveness [148].

573 The effect of quantization errors can be observed by treating the inputs and outputs of a computing 574 system as real-valued analog signals and comparing these signals to an ideal (error-free) computing 575 system that accepts analog inputs and produces analog outputs. When such ideal outputs are not 576 available, designers often use the output of the highest precision available (e.g., double-precision 577 floating point) as the reference from which to determine the error of a reduced-precision block. 578 Such analyses are common in the design process of digital signal processing algorithms such as 579 filters [159] where the choice of number representation and quantization level enables a tradeoff 580 between the performance and signal-to-noise ratio properties of a system. 581

#### 582 Analog computing: data processing with currents and voltages 5.3

Analog computing systems [103, 130] eliminate the need for discretization and the resulting 583 restriction on precision that is inherent in digital circuits. While, in theory, analog circuits provide 584 585 unbounded precision, in practice their precision is limited by factors such as noise, non-linearities, the degree of control of properties of circuit elements such as resistors and capacitors, and the 586 degree of control of implicit parameters such as temperature. At higher precision, analog blocks tend 587

to be less energy-efficient than digital blocks of equivalent precision [186]. Because they usually do

not use minimum-size transistors, analog circuits may also be larger in area than their digital circuit

equivalents. Designing analog computation units is also a challenging task. Nevertheless, analog

circuits can be an attractive solution for applications that tolerate low-precision computation [186].

# 5.4 Probabilistic computing: exploiting device-level noise for efficiency

A line of research pioneered by Palem et al. [35, 156] ("probabilistic computing") proposes harnessing 595 intrinsic thermal noise of CMOS circuits to improve the performance of probabilistic algorithms 596 that exploit a source of entropy for their execution. Chakrapani et al. [31] show an improvement in 597 the energy-performance product for algorithms such as Bayesian inference, probabilistic cellular 598 automata, and random neural networks using this approach and they establish a tradeoff between 599 the energy consumption and the probability of correctness of a circuit's behavior. These techniques 600 have also shown energy savings for digital signal processing algorithms that do not employ 601 probabilistic algorithms but which can tolerate some amount of noise [67, 107]. 602

# 5.5 Stochastic computing: unary representation and computing on probabilities

604 Stochastic computing (SC) uses a data representation of bit streams that denote real-valued proba-605 bilities [6]. In theory, the probabilities can have unbounded precision, but in practice, the length of 606 the bit-streams determines precision [4]. SC was first introduced in the 1960s [65] and its main 607 benefit is that it allows arithmetic operations to be implemented via simple logic gates: a single AND 608 gate performs SC multiplication. This made SC attractive in the era of expensive transistors. But as 609 transistors became cheaper, SC's benefit faded away, and its main drawbacks, i.e., limited speed 610 and precision, became dominant [4]. For this reason, SC was only used in certain applications, such 611 as neural networks [51, 111] and control systems [223]. 612

SC has seen renewed interest over the last decade [4], mainly because of its energy efficiency. SC's probabilistic nature copes with new inherently random technologies such as memristors [112]. Furthermore, the unary encoding of numbers on SC makes the computation robust against errors [160], and allows variable precision computation [5]. With the low precision requirement of modern machine learning applications, SC is becoming an attractive alternative to conventional binary-encoded computation [119].

Despite what the name suggests, most existing SC circuits are in fact deterministic. Unless a true random number source (e.g., memristors) is used, SC circuits will produce the same output if inputs are unchanged. Although pseudo-random number generators with long periods can imitate a true random number source, in reality they are still deterministic. Furthermore, several studies have shown that adding determinism to SC is in fact useful [75, 151]. If carefully chosen, deterministic number sources can increase the accuracy of SC circuits without adding any extra overhead.

# 5.6 Voltage overscaling: improved efficiency from reduced noise margins

The term *voltage overscaling* is often used to refer to reducing supply voltages more than is typically deemed safe for a given clock frequency. Voltage overscaling exploits the quadratic relationship between supply voltages and dynamic power dissipation. Let  $V_{dd}$  be the supply voltage of a CMOS circuit (e.g., an inverter), let f be its clock frequency (reciprocal of its delay) and let C be the effective capacitance of the load of the circuit. Then, the dynamic power dissipation P is [162]

$$P \propto C V_{\rm dd}^2 f.$$

(1)

The delay of a gate in a circuit, and hence the clock frequency f, is however not independent of supply voltage  $V_{dd}$ . Let  $V_t$  be the device threshold voltage and let  $\alpha$  be a process-dependent parameter (the velocity saturation exponent [176]). Then, as supply voltage  $V_{dd}$  decreases, the delay of charging its load capacitance for a gate increases and the maximum clock frequency achievable

593

594

603

613

614

615

616

617

618

619

620

621

622

623

624 625

626

627

628

629

630

639 640 Stanley-Marbell et al.

at a given voltage follows the relation

$$f \propto \frac{(V_{\rm dd} - V_t)^{lpha}}{V_{\rm dd}}.$$

(2)

641 As a result, overscaled voltages cause circuit delays, which in turn lead to timing errors in circuits 642 at a fixed clock speed. Several approaches have explored the idea of carefully and systematically 643 accepting such errors in exchange for the large (quadratic) power savings that voltage overscaling 644 can potentially provide [84, 100, 102, 114, 196]. In unmodified circuits, this often leads to catastrophic 645 errors at close-to-nominal voltages, as many digital circuits are optimized to minimize timing slack. 646 However, for several application domains, such as image and video processing, inherent dependence 647 of errors on known input characteristics can be exploited to redesign circuits such that they allow 648 for significant overscaling with small and graceful degradation of output quality [13, 81, 147, 649 225]. However, voltage overscaling has potential issues with timing closure and meta-stability. 650 Furthermore, timing errors in the critical paths of a circuit due to voltage overscaling tend to affect 651 the most significant bits of a computation first and hence can lead to large errors. Dedicated logic 652 modifications targeting lower significant bits as described next can instead provide better accuracy 653 with additional switching activity savings for the same timing and hence voltage reduction [137]. 654

# 5.7 Pruned circuits for efficiency at the expense of precision and accuracy

Pruning circuits refers to deleting or simplifying parts of a circuit based on the probability of their

usage or importance to output quality. Recent research has shown how circuit pruning improves

latency, energy, and area without the overheads associated with voltage scaling [122, 136, 189, 197].

Pruning can be applied to digital circuit building blocks such as adders and multipliers, enabling 659 quality-cost tradeoff opportunities through different logic simplification and pruning techniques. 660 Approximate adders attempt to simplify carry chains [232, 243] or to use approximate 1-bit full 661 adders [76, 131, 137] at lower significant digits of a sum computation. Accuracy-configurable adders 662 have also been proposed for adaptive-accuracy systems that require a functional unit like an adder 663 or multiplier to vary the degree of tradeoff between correctness and resource usage based on the 664 quality demand of computation [99]. Unlike approximate adders, approximate multipliers have a 665 higher design space exploration requirement, as they are composed of 2×2 partial products that 666 are summed up by deploying an adder tree to compute the final result [113]. Correctness versus 667 resource usage tradeoffs can be deployed in multipliers (partial products) or adders, or both, for a 668 chosen number of least-significant bits [95, 170]. 669

Approximate adders and multipliers provide the combinational building blocks for approximate 670 datapath and processor designs. At the sequential logic level, the challenge is in determining 671 the amount of approximation to apply to each addition or multiplication operation in a larger 672 computation in order to minimize output quality loss while maximizing energy savings. For 673 example, in a larger computation that consists of multiple accumulations, using an adder with a 674 zero-centered error distribution [137] will result in positive and negative errors canceling each other 675 and thus averaging in the final output of a larger accumulation. Similarly, approximate multipliers 676 with unbiased error distribution are promising for accumulation-based algorithms like multiply-677 accumulate (MAC) [80]. By contrast, in other computations, an approximate combinational block 678 679 that always over- or under-estimates may be beneficial.

Determining the best tradeoff for each functional unit in a larger sequential design has been investigated for fixed register transfer level (RTL) designs [152, 166, 231]. Pure RTL optimizations, on the other hand, do not exploit changes in approximated component characteristics for a complete RTL re-design. In the context of custom hardware/accelerator designs, selection of optimal approximated operator implementations can instead be folded into existing C-to-RTL high-level synthesis (HLS) tools [118, 120]. For programmable processors, accuracy configuration of the datapath can

be exposed through the instruction-set architecture (ISA) [229]. A compiler then has to determine

the precision of each operation in a given application (see Section 6 and Section 7).

# 5.8 Approximate memory: reducing noise margins for efficiency in storage

690 Memory costs are often higher than that of computations in many data-intensive applications [15]. 691 Approximate memories have been investigated in the research literature, to trade quality for 692 energy, latency, and lifetime benefits [181, 198]. Reducing the refresh rate of DRAM provides an 693 opportunity to improve energy efficiency while causing a tolerable loss of quality [98, 165]. For 694 static random access memory (SRAM), by contrast, the tradeoff between correctness and resource 695 usage is typically achieved by voltage overscaling, where the main concern is in dealing with the 696 failures in the standard 6-Transistor (6T) cells of an SRAM array under reduced static noise margins 697 (SNMs) [66]. As a result, hybrid implementations combining 6T with 8T SRAM cells [32] or with 698 standard cell memory (SCMEM) [19] have been employed to achieve aggressive voltage scaling in 699 order to get better quality versus cost tradeoffs. In case of emerging non-volatile random-access 700 memory (NVRAM) technologies, such as spintronic memories (e.g., STT-MRAM), reducing the read 701 current magnitude can reduce energy of read operations at the expense of reduced noise margins 702 and hence accuracy of the content being read [167]. Similarly, significantly increasing the read 703 current magnitude reduces the read pulse duration, decreasing the read latency while potentially 704 disturbing the written content with noise. 705

# 706 5.9 Summary

The circuit-level techniques surveyed in this section must ultimately be deployed in the context of 707 concrete applications. For example, one case study found that for applications such as Fast Fourier 708 Transforms (FFTs), motion compensation filters, and k-means clustering, applying traditional 709 fixed-point optimizations to limit the size of operands was more effective than applying circuit-710 level approximations such as approximate adders and multiplier circuits [14]. This is because 711 approximating some bit values still requires information about those bits to be stored and used in 712 downstream computations. The additional overhead of this bookkeeping in many cases is not worth 713 the quality benefits. Carefully selecting the most suitable approximation strategies and comparing 714 their cost versus quality tradeoffs can therefore lead to a better solution for certain applications. 715

# <sup>716</sup> 6 ARCHITECTURE AND MICROARCHITECTURE-LEVEL TECHNIQUES

Architectural and microarchitectural techniques that trade correctness for resource usage have

focused primarily on correctness at the software or application level and have focused on reducing

resource usage in memory, in the processor, and in on- or off-chip I/O.

# 721 6.1 Notation

Architectural techniques create abstractions that allow operating systems, programming languages, 722 and applications to specify their precision and accuracy requirements through specialized instruc-723 tions and instruction extensions. Following the notation introduced in Section 4, the computation 724 function  $f : \mathbb{Q}^m \to \mathbb{Q}^o$  is defined over the quantized sets  $\mathbb{Q}^m$  and  $\mathbb{Q}^o$  embodied by software-visible 725 machine state such as registers, memory, and storage. The computation function f is implemented 726 using either general-purpose cores or specialized hardware accelerators. Microarchitectural tech-727 niques facilitate the efficient implementation of the computation function f at the level of hardware 728 functional units, such as memory controllers and processor pipelines, or by the efficient hardware 729 representation of the sets  $\mathbb{Q}^m$  and  $\mathbb{Q}^o$ . 730

# 6.2 Trading resource usage for correctness in processor cores

Early work trading resource usage for correctness such as Razor and related techniques [57, 202], relied on voltage overscaling as the primary underlying circuit-level mechanism to increase

energy efficiency. As a result, these techniques provided no direct means to improve performance,

735

but provided higher energy efficiency at the expense of nondeterministic faults. To mask such

faults and hide them from applications, voltage overscaling approaches typically rely on error

recovery mechanisms. The key insight is that sophisticated error recovery mechanisms can be much

more resource-efficient in ensuring correctness compared to voltage over-provisioning. Carefully

balancing the error recovery overhead against the benefits of voltage overscaling can provide

higher energy efficiency without sacrificing output quality or program safety [57, 202].

Truffle [58] was the first architecture to willingly introduce uncorrected nondeterministic errors 742 in processor design for the sake of energy efficiency. Truffle uses voltage overscaling selectively to 743 implement approximate operations and approximate storage. The Truffle architecture provides ISA 744 extensions to allow the compiler to specify approximate code and data and its microarchitecture 745 provides the implementation of approximate operations and storage through dual-voltage operation. 746 For error-free operations, a high voltage is used, while a low voltage can be used for approximate 747 operations. Voltage selection is determined by the instructions, with the control-flow and address 748 749 generation logic always operating at a high voltage to ensure safety.

In addition to improving energy efficiency, architectures that enable tradeoffs between resource 750 usage and correctness may result in higher performance compared to an error-free baseline [59, 751 150, 204, 238]. Examples of approaches include offloading parts of a processor's workload to 752 computing units that can perform the desired functionality much faster at the cost of deviation 753 from correct behavior. Because of their performance advantage, such computing units are often 754 called accelerators. Accelerators that trade resource usage for correctness include, most notably, 755 neural accelerators [59, 150, 204, 238], which implement a hardware neural network trained to 756 mimic the output of a desired region of code. 757

Temam et al. empirically show that the conceptual error tolerance of neural networks translates 758 into the defect tolerance of hardware neural networks [220], paying the way for their introduction 759 in heterogeneous processors as intrinsically error-tolerant and energy-efficient accelerators. St. 760 Amant et al. demonstrate a complete system and toolchain, from circuits to a compiler, that 761 features an area- and energy-efficient analog implementation of a neural accelerator that can be 762 configured to approximate general purpose code [204]. The solution of St. Amant et al. comes 763 with a compiler workflow that configures the neural network's topology and weights. A similar 764 solution was demonstrated with digital neural processing units, tightly coupled to the processor 765 pipeline [59], delivering low-power approximate results for small regions of general-purpose code. 766 Neural accelerators have also been developed for GPUs [238], as well as FPGAs [150]. 767

### 769 6.3 Approximate memory elements

Memory architectures that trade resource usage for correctness permit the value that is read from 770 a given memory address to differ from the most recent value that was written. The traditional view 771 of memory elements assumes that every memory access pair consisting of a write followed by a 772 subsequent read operation, applied to a input I, results in the same read result for a given write 773 value. In contrast, approximate memory elements may perform non-identity transformations of 774 the input I. At the architecture level, the benefits of doing so are exposed and leveraged through 775 reduced read/write latency, reduced read/write access energy, fewer accesses to memory, increased 776 read/write bandwidth, increased capacity [74, 94, 181], improved endurance [181], and reduced 777 leakage power dissipation [125]. These techniques have been applied to memory components 778 ranging from CPU registers [58], caches [58, 183–185], main memory [125], to flash storage [74, 94, 779 181]. 780

Underlying memory technologies employ circuit-level mechanisms to trade accuracy for reduc tion in latency or access energy (or both) (see Section 5.8). Exposing such mechanisms as tunable

knobs to the architecture allows adaptive selection of different approximation/efficiency operation

points to better fit varying application requirements. For volatile memory technologies, such as 785 SRAM and DRAM, voltage scaling and refresh rate scaling can be used to reduce static or dynamic 786 787 energy at the expense of faults, observed as bit flips [58]. In the case of DRAM, differentiating between rows that contain data for which errors can be tolerated versus rows that applications re-788 quire to remain correct motivates selective refresh rate reduction approaches [125]. In non-volatile 789 memories, mechanisms that reduce read or write noise margins for energy gains can be leveraged 790 791 at the architectural level through dedicated instructions for imprecise loads and stores [167]. For 792 multi-level solid-state memories that perform write operations iteratively until the written value is 793 in the desired range, reducing the number of write iterations significantly reduces the latency and energy of such approximate writes [181], increasing write bandwidth as a side effect, at the expense 794 of reduced data retention. Furthermore, mapping data that applications can tolerate to be incorrect 795 onto blocks that have exhausted their hardware error correction resources can significantly extend 796 797 endurance.

798 Other architectural methods for trading resource usage for correctness in memories include predicting memory values instead of performing an actual read operation. For example, on the 799 occurrence of a cache miss, load value approximation (LVA) [185, 221] provides predicted data 800 values to a processor which may differ from the correct values in main memory. Doing so hides 801 cache miss latency and thereby reduces the average memory access time at the expense of having 802 803 data values in the cache that differ from what they would be had they been faithfully loaded from main memory. The correct values in main memory may subsequently be read from memory to 804 train the predictor and improve its accuracy, or the main memory access may be skipped entirely 805 to save energy. Conventional value prediction considers any execution relying on predicted values 806 speculative and provides expensive microarchitectural machinery to roll back execution in the 807 case of a mismatch between the predicted and actual values. LVA, by contrast, allows imperfect 808 predictions, trading correctness of values in the cache for reduced micro-architectural complexity 809 and reduced memory latency. 810

The correctness of values obtained from memories can also be traded for an increase in effective 811 storage capacity. One way to achieve this is to avoid storing similar data multiple times. For example, 812 storing similar data in the same cache line can save on cache space in situations when substituting 813 a data item for a similar one still yields acceptable application quality [183, 184]. Another way to 814 trade errors for capacity is through deliberate reduction in storage resources dedicated to error-815 correction [74, 94]. By providing weaker error-correction schemes for data whose accuracy does 816 not have a critical impact on the output quality, significant storage savings have been demonstrated 817 in the case of encoded images and videos [74, 94]. 818

### 820 6.4 Approximate communication

As in the case of approximate memory elements, approximate communication systems may perform 821 non-identity transformation  $f^*$  of input I to efficiently transfer the input through a communication 822 channel or network. The idealized computation function f corresponds to an identity transformation 823 over an infinitely large input. Examples of inputs include signals on intra- and inter-chip wires, 824 such as memory buses and on-chip networks. The architectural techniques trading resource usage 825 for correctness in such systems usually rely on more efficient but less reliable links, network buffers, 826 and other network elements, or employ lossy in-network compression to minimize data movement, 827 while overlapping the compression and communication. 828

The conventional approach to trade resource usage for correctness in communication over a channel is to employ lossy compression at the source and decompression at the destination, with the goal of reducing the amount of data transferred through the channel, as well as to reduce latency. Such approaches have been widely used for decades in long-distance communication, such

833

as media streaming applications. However, when the communicating parties are two processors on

a board, two cores on a chip, or a core and a cache, the communication latency is in the order of

nanoseconds and any compression/decompression latency added to the critical path of program

execution may be prohibitive.

At the circuit level, transmitting bits over a wire on-chip or over a printed circuit board trace costs 838 energy. For single-ended I/O interfaces, where the signaling of information is with voltage levels, 839 the energy cost is typically due to the need to charge the wire capacitance when driving a logic '1', 840 841 and to discharge that capacitance when driving a logic '0'. Building on this observation, and on the body of work on low-power bus encodings [38, 205], value-deviation-bounded serial encoding 842 (VDBS encoding) [212, 214] trades correctness for improved communication energy efficiency by 843 lossy filtering of values to be transmitted on an I/O link. VDBS encoding reduces the number of 844 '0' to '1' and '1' to '0' signal transitions and hence reduces the energy cost of I/O. Because VDBS 845 encoding requires no decoder, it can be implemented with low overhead, requiring less than a 846 847 thousand gates for a typical implementation [208]. Extensions of VDBS encoding have extended the basic concept to exploit temporal information in information streams [109, 155] and to employ 848 probabilistic encoding techniques [209]. 849

A recent study leverages data similarity between cache blocks to perform lossy compression in networks-on-chip (NoCs) [22]. The key idea is in simple data-type aware approximation using approximate matching between data to be sent and data items that have been recently sent to perform a quick lossy compression. Performing approximation at the network layer allows a significant data movement reduction without losing the precise copy of the data and without extending the critical path, as the communication and compression are overlapped.

An orthogonal approach to trading resource usage for correctness in communication by com-856 pression, is to reduce the safety margins of communication links to trade off their reliability for 857 bandwidth, latency, or both. For on-chip networks, achieving reliable transmission in low-latency 858 high-bandwidth interconnects requires features like forward error correction (FEC), but FEC can 859 increase communication latency, by up to three fold in one study [64]. An approach to counteract 860 such high overheads is to allow higher bit error rates at the link layer by removing forward error 861 correction or employing a weaker but more efficient error correction mechanisms, with a variable 862 amount of redundancy based on application needs [64]. A low-diameter network is one approach 863 to keep the end-to-end bit error rate under control, minimizing the number of hop counts, and thus 864 prevent excessive accumulation of errors [64]. 865

Allowing errors in communication can be particularly challenging in parallel programs, which 866 rely on communication for synchronization. In such contexts, failure to deliver correct messages on 867 time can affect control flow and lead to catastrophic results [241]. Yetim et al. propose a mechanism 868 to mitigate inter-processor communication errors in parallel programs by converting potentially 869 catastrophic control flow or communication errors into likely tolerable data errors [241]. Their 870 main insight is that data errors have much less impact on the application output compared to errors 871 in control flow. Their approach is to monitor inter-processor communication in terms of message 872 count, and to ensure that the number of communicated items is correct, either by dropping excess 873 874 packets or by generating additional packets with synthetic values. Ensuring the correct number of exchanged messages improves the integrity of control flow in the presence of communication 875 errors and consequently improves the output quality of approximate parallel programs. 876

### 878 6.5 Summary

Microarchitectural techniques that trade correctness for resources build on circuit level techniques (Section 5) to exploit information at the level of hardware structures such as caches, register files, off-chip memories, and so on. Architectural techniques expose microarchitectural techniques

882

to software through constructs such as instruction extensions, new instruction types, or new 883 hardware interfaces to accelerators. Exposing information about hardware techniques to software 884 allows software to take advantage of the implemented techniques, while exposing information from 885 software to hardware allows hardware to, for example, more aggressively leverage tradeoffs between 886 correctness and resource usage. In the same way that circuit-level techniques form a foundation 887 for the approaches discussed in this section, circuit-level, microarchitectural, and architectural 888 techniques similarly form a foundation for operating system and runtime system techniques. 889

#### 7 **PROGRAMMING LANGUAGE TECHNIQUES**

891 Many programming-language- and compiler-level techniques that trade correctness for efficiency 892 provide abstractions for dealing with errors introduced at lower levels of the system stack, or 893 introduce higher-level approximations directly and these errors combine into whole-application 894 errors. Previous research presented a variety of automated transformations, together with the 895 reasoning mechanisms that verify or estimate the accuracy of the whole-application results. 896

This section focuses on the techniques for *reasoning* about approximations and *managing* their 897 impact on program execution. We divide the techniques into two broad categories: (1) static compile-898 time techniques ensure that tradeoffs are safe to apply for all inputs, without running a program 899 and (2) dynamic tuning techniques typically execute the program on a set of representative inputs to 900 estimate the benefit and safety of the transformations (off-line), or monitor the program execution 901 at runtime to tune the level of approximation (on-line). 902

#### 7.1 Notation

890

903

904 Following the notation introduced in Section 4, programming language techniques usually operate 905 at a level of abstraction where the computation's implementation  $f : \mathbb{I} \times \mathbb{O}$  is defined over a sets 906 represented by, e.g., integers or floating-point numbers. These integer and floating-point number 907 representations serve as an abstraction for the actual bit-level representations of program state 908 in hardware. The idealized specification  $f^*$  that f implements may thus, for instance, assume 909 unbounded integers or real numbers for its output  $\mathbb{O}$  and may represent an entire computational 910 problem or specific algorithm. Examples of errors introduced by the discrepancy between f and 911  $f^*$  are floating-point roundoff errors, errors due to skipping entire portions of a computation or 912 due to missing synchronization. To quantify the end-to-end error, a developer typically specifies 913 a distance  $d(f, f^*)$ . Examples distances include absolute error, relative error, worst-case error, 914 or error probability. Selecting the appropriate distance and its acceptable threshold are typically 915 application-dependent. 916

#### 7.2 Static compile-time techniques 917

Static techniques aim to make resource versus correctness tradeoffs safe to apply without having to 918 run a program. Safety of approximate programs ensures that (1) the errors caused by the approxi-919 mation never make the program crash, diverge, or violate other important program properties, and 920 (2) the result of the approximation is acceptable, i.e., that the magnitude and frequency of errors 921 is within certain bounds. Errors introduced at the lower levels of the stack do not affect every 922 operation of a high-level program equally. Ideally, errors in lower layers of the stack should be 923 restricted to locations such that when they propagate to higher layers of the stack, they only affect 924 those parts of the program where errors can be tolerated. 925

Conventional programming languages, however, do not provide a transparent way to mark what 926 can be potentially approximate. Several approaches propose annotations that allow the developer 927 to make the effects of lower-level errors explicit: EnerJ [180] ("approx" and "precise" data types), 928 Asymmetric RHL [20, 29] ("relax" and "relate" variable annotations), and FlexJava [158] ("loosen" 929 and "tighten" variable annotations). These techniques use type inference, theorem proving, and 930